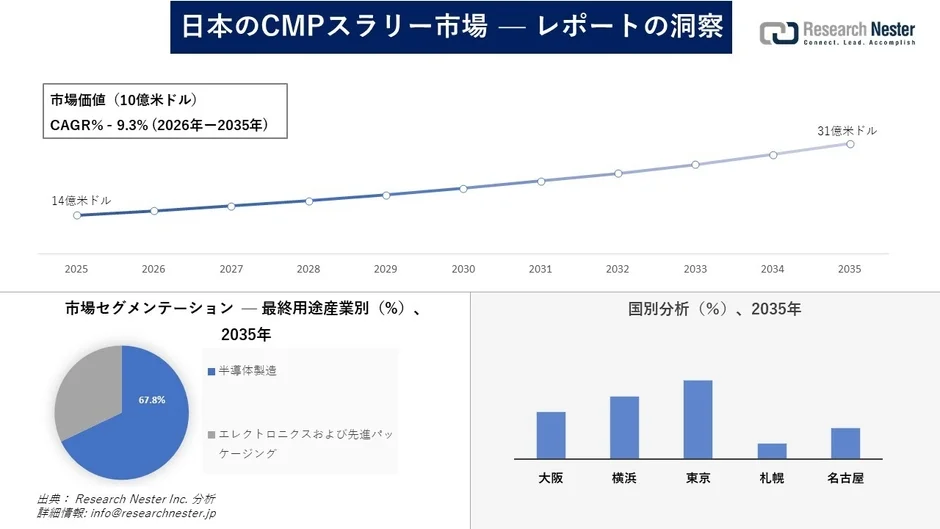

日本のCMPスラリー市場、半導体製造の進展と政府投資により大幅な成長を予測

Research Nester Analyticsが実施した最新の調査「日本のCMPスラリー市場」によると、国内のCMPスラリー市場は2025年に14億米ドルと評価され、2035年末には31億米ドルに達すると予測されています。この予測期間中(2026年〜2035年)の年平均成長率(CAGR)は9.3%と見込まれており、2026年末までには市場規模が15億米ドルに達すると予想されています。

市場成長の主要因はSiCの採用増加と技術革新

市場の成長を牽引している主な要因の一つは、先進的な半導体アプリケーションにおけるシリコンカーバイド(SiC)の採用増加です。SiCは、従来のシリコンと比較して、より高い熱伝導率、広いバンドギャップ、向上した電子移動度などの優れた特性を提供するため、自動車、航空宇宙、エネルギー分野における高出力および高周波デバイスに最適であるとされています。

SiCウェハの使用が増加するにつれて、化学機械研磨(CMP)のような精密な表面仕上げ技術の必要性が高まっています。特に、酸化アルミニウムと二酸化マンガンを含む最適化されたスラリー組成におけるCMPプロセスの実験的な進展は、材料除去率の向上と超低表面粗さを実現し、ウェーハ処理の効率を高めています。これらの技術的改善が、日本の半導体製造エコシステムにおける高性能CMPスラリーソリューションの需要を促進している状況です。

主要企業の最新動向

日本のCMPスラリー市場では、最近いくつかの重要な動きが見られます。

-

FUJIFILM Corporation: 2025年9月、複数の半導体チップを一つのパッケージに統合する先進的なパッケージング用CMPスラリーの発売を発表しました。この製品は、AI半導体の性能向上に不可欠な先進パッケージング技術であるハイブリッドボンディングにおける接合面平坦化のための研磨剤として、大手半導体デバイスメーカーに採用されています。

-

KCTech: 2025年8月、世界の半導体大手企業に対し、先進的なCMP装置およびスラリーの供給を開始しました。同社は、ウェーハの品質、精度、製造歩留まりの向上を実現する統合ソリューションを提供し、各企業のニーズに応じたソリューションを提供しています。

半導体製造が市場を牽引、東京が成長の中心地

最終用途産業別では、半導体製造セグメントが2035年までに67.8%の最大市場シェアを獲得すると推定されています。この優位性は、経済産業省を通じた政府主導の半導体再活性化への投資によって強力に支えられています。2023年11月の世界経済フォーラムのデータによると、国内半導体生産の強化とサプライチェーンの強靭性を確保するために130億ドル以上が約束されています。これには、TSMCの日本工場やRapidusの先進的な2nmチッププロジェクトなどの主要プロジェクトへの資金提供が含まれており、ウェーハ処理の要件を大幅に増加させています。

地域別では、東京が予測期間中に最大の市場シェアを占めると予想されています。これは、日本の半導体製造エコシステムの拡大と、先進的なチップ生産への政府の継続的な投資に支えられています。ITAの2025年11月のデータによると、日本の半導体市場は2025年までに510億米ドルを超えると推定されており、主にロジックおよびメモリICの製造への投資の増加によって推進されています。

さらに、日本は2030年までに半導体およびAI開発のために628億米ドル以上のより広範な戦略的コミットメントを発表しており、ウェハー製造施設の拡大を促進しています。高精度なウェハ研磨プロセスが必要とされる先進的なノード製造は、CMPスラリーの消費に大きな影響を与えています。

市場の主要プレーヤー

日本のCMPスラリー市場における主なプレーヤーは以下の通りです。

-

Fujimi Incorporated

-

Resonac Corporation

-

JSR Corporation

-

AGC SEIMI CHEMICAL Co., Ltd.

-

Shin Etsu Chemical Co., Ltd.

調査レポートの詳細情報

この調査レポートに関する詳細な洞察は、以下のResearch Nesterのウェブサイトで確認できます。

コメント